Tartalomjegyzék:

- 1. lépés: PWM modul- forrásfájl létrehozása

- 2. lépés: PWM modul építése- Vivado Setup

- 3. lépés: PWM modul felépítése- Hozzon létre egy projektfájlt

- 4. lépés: PWM modul felépítése- Blokktervezés és kényszerfájl beállítás (I)

- 5. lépés: PWM modul felépítése- Blokktervezés és kényszerfájl beállítás (II)

- 6. lépés: PWM modul felépítése- Blokktervezés és kényszerfájl beállítás (III)

- 7. lépés: PWM modul felépítése- Blokktervezés és kényszerfájl beállítás (IV)

- 8. lépés: PWM modul felépítése- Blokktervezés és kényszerfájl beállítás (V)

- 9. lépés: PWM modul felépítése- Hardver telepítése

- 10. lépés: PWM-modul létrehozása- Bitfolyam létrehozása és SDK indítása

- 11. lépés: PWM modul létrehozása- Hozzon létre egy új alkalmazást a Xilinx SDK-ban

- 12. lépés: PWM modul felépítése- A Project Explorer áttekintése (I)

- 13. lépés: PWM modul felépítése- A Project Explorer áttekintése (II)

- 14. lépés: PWM modul felépítése- A Project Explorer áttekintése (III)

- 15. lépés: PWM modul felépítése- PWM funkció (I) csomagolása

- 16. lépés: PWM modul felépítése- PWM funkció (II) csomagolása

- 17. lépés: PWM-modul felépítése- PWM-funkció (III) csomagolása

- 18. lépés: PWM modul építése- futtassa

- 19. lépés: Streaming Video Processing on Digilent ZYBO with OV7670

- 20. lépés: Töltse ki a blokkdiagramot

- 21. lépés: Csatlakoztassa az OV7670 -et a ZYBO -hoz

- 22. lépés: Blokktervezés létrehozása

- 23. lépés: VHDL -fájlok hozzáadása az OV7670 kameravezérléshez és rögzítéshez

- 24. lépés: Kényszerfájl hozzáadása

- 25. lépés: IP -repó hozzáadása a HLS IP -hez

- 26. lépés: Modulok és IP hozzáadása

- 27. lépés: IP -konfigurációs beállítások

- 28. lépés: A PS IP -blokk hozzáadása és konfigurálása

- 29. lépés: 1. rész: PWM modul építése szervomotorokhoz

- 30. lépés: Videó bemeneti oldali csatlakozók (kiemelve)

- 31. lépés: Csatlakozások az OV7670 -hez

- 32. lépés: Csatlakozások a videó kimeneti oldalon

- 33. lépés: Futtassa a blokkolás és a kapcsolat automatizálását

- 34. lépés: Hozzon létre HDL csomagolót

- 35. lépés: Bitfolyam létrehozása, hardver exportálása SDK -ba, SDK indítása a Vivado -ból

- 36. lépés: SDK (nincs FreeRTOS)

- 37. lépés: FreeRTOS implementáció

- 38. lépés: Használati utasítások

- 39. lépés: Hivatkozások és hivatkozások

- Szerző John Day day@howwhatproduce.com.

- Public 2024-01-30 09:43.

- Utoljára módosítva 2025-01-23 14:48.

Kezdje az első lépéssel a 2 tengelyes szervo PWM vezérlő létrehozásának részleteiről.

Kezdje a teljes projekt nagy tömbvázlatával (19. lépés).

Kamera + pan/tilt beállítás, amit használtunk:

A Digilent PmodCON3 -at használták a szervók csatlakoztatására.

1. lépés: PWM modul- forrásfájl létrehozása

2. lépés: PWM modul építése- Vivado Setup

Először töltse le a Vivado Design Suite programot a Xilinx webhelyről. Telepítse az összes tervezőcsomagot, beleértve a Vivado szoftverfejlesztő készletet (SDK). Ez a projekt a 2017.2 -es verziót használja.

Addig is a Digilent Adept 2 -t Zybo kártya illesztőprogramként kell telepíteni.

3. lépés: PWM modul felépítése- Hozzon létre egy projektfájlt

A projektfájl létrehozása előtt győződjön meg arról, hogy a Zybo fájlt már megfelelően telepítette az oktatóanyagként:

Vivado 2015.1 verzió és későbbi kártyafájl telepítése

Nyissa meg a Vivado 2017.2. A gyorsindításban kattintson a Projekt létrehozása -> Következő -> Projekt neve (Itt adja meg a projekt nevét) -> Projekt típusa elemre. A Projekt típusa területen válassza az RTL Project lehetőséget, és jelölje be a „Ne adja meg a forrásokat jelenleg” lehetőséget. Ezután az alapértelmezett résznél válassza ki a „Boards” és a „Zybo” megjelenítési nevet. Ezután kattintson a Befejezés gombra a projekt elindításához.

4. lépés: PWM modul felépítése- Blokktervezés és kényszerfájl beállítás (I)

A Flow Navigator alkalmazásban kattintson a „Blokkterv létrehozása” elemre, majd nyomja meg az OK gombot. kattintson a „+” jelre a szükséges IP -címek hozzáadásához. Hozzáadás:

- Egy ZYNQ7 feldolgozó rendszer Két AXI időzítő

- Két AXI időzítő

5. lépés: PWM modul felépítése- Blokktervezés és kényszerfájl beállítás (II)

IP -címek hozzáadása után futtassa a blokk -automatizálást és a kapcsolat -automatizálást. Miután az automatizálás befejeződött, az „axi_timer_0” blokkon kattintson a jobb gombbal a pwm0 -> Make External elemre. Nevezze el a pwm0 külső tűt pwm_Xaxis néven. Ismételje meg a fenti folyamatot az „axi_timer_1” blokkon, és nevezze el a pwm0 külső tűt pwm_Zaxis -nak.

6. lépés: PWM modul felépítése- Blokktervezés és kényszerfájl beállítás (III)

Vegyük észre, hogy minden alkalommal, amikor befejezzük a blokktervezést Vivadóban, létre kell hoznunk egy HDL csomagolót. Mivel ez lesz minden projekt felső szintű modulja.

7. lépés: PWM modul felépítése- Blokktervezés és kényszerfájl beállítás (IV)

Most be kell állítanunk a kényszerfájlt, hogy hozzárendelhessük a tömbvázlatunkhoz csatlakoztatott csapokat. Zárja be a Blokktervezés ablakot, a Források lapon, a „Források hozzáadása”-> Kényszerek hozzáadása vagy létrehozása-> adja hozzá a Zybo-Master.xdc fájlt korlátozó fájljainkhoz.

8. lépés: PWM modul felépítése- Blokktervezés és kényszerfájl beállítás (V)

Nyissa meg a Zybo-Master.xdc kényszerfájlt a Constraints mappából, vegye ki a megjegyzéseket azokból a portokból, amelyeket kimeneti jelekként kívánunk megadni, és nevezze át a „get_ports {XXXX}” nevet, amely XXXX a blokkdiagramban megnevezett külső tűt jelöli. A kényszerfájl beállítása az ábrán látható.

9. lépés: PWM modul felépítése- Hardver telepítése

Csatlakoztassa a szervomotorokat a Pmod CON3 -hoz. A TowerPro SG90 a szervomotoros modell, amelyet ebben a projektben használtunk. A szervomotoros vezetékeknél a narancssárga vezeték a PWM jelet jelöli, amely a Pmod CON3 SIG érintkezőjéhez van csatlakoztatva. A piros Vcc vezeték a Pmod CON3 VS csapjához csatlakoztatott tápkábel. Végül a barna Gnd vezeték a GND csaphoz csatlakoztatott földelő vezeték. Ezután helyezze be a Pmod CON3 -at a Zybo Board JD portjának felső sorába.

10. lépés: PWM-modul létrehozása- Bitfolyam létrehozása és SDK indítása

1. A Project Navigator lapon futtassa a BitStream generálása lehetőséget.

2. Hardver exportálása: Fájl> Exportálás> Hardver exportálása-> jelölje be az „include bitstream” lehetőséget-> OK 3. Indítsa el az SDK-t: Fájl-> Indítsa el az SDK-t.

11. lépés: PWM modul létrehozása- Hozzon létre egy új alkalmazást a Xilinx SDK-ban

Hozzon létre egy új alkalmazást:

Fájl> Új> Alkalmazásprojekt -> Írja be a projekt nevét -> Befejezés

A Project Explorer alatt három mappának kell lennie.

Ebben az esetben a „design_1_wrapper_hw_platform_0” a Vivado által korábban exportált mappa. Az Axis_2_PWM_SDK_bsp az alaplap támogatási csomagja. Az Axis_2_PWM_SDK pedig a fő projektmappa az SDK -ban. A „helloworld.c” fájl látható az Axis_2_PWM_SDK „src” mappájában, ahol a „helloworld.c” a fő fájl.

12. lépés: PWM modul felépítése- A Project Explorer áttekintése (I)

Nézzünk meg néhány fájlt a Project Explorer alatt. Először a „design_1_wrapper_hw_platform_0” mappában nyissa meg a „system.hdf” fájlt. Ez a fájl a ps7_cortex9 processzor címtérképét és a tervezésünkben szereplő IP -blokkokat mutatja be.

13. lépés: PWM modul felépítése- A Project Explorer áttekintése (II)

Ezután ellenőrizze az „include” és a „libsrc” fájlokat az „Axis_2_PWM_SDK_bsp” mappában. Az itt található könyvtári fájlok lehetővé teszik számunkra, hogy a regiszterek „lejátszása” nélkül lépjünk kapcsolatba a hardver perifériákkal.

14. lépés: PWM modul felépítése- A Project Explorer áttekintése (III)

A BSP dokumentációján keresztül az xtmrctr.h Xilinx Timer Control Library néven található, amely az AXI Timerhez kapcsolódik. Itt általában megtaláljuk a kívánt PWM funkciót. Ha azonban elolvassa a „tmrctr_v4_3” dokumentációt, az azt mutatja, hogy az illesztőprogram jelenleg nem támogatja az eszköz PWM működését. A PWM funkció hiányossága miatt be kell fejeznünk a PWM funkciónkat az xtmrctr.h és az AXI Timer v2.0 LogiCORE IP Product Guide segítségével.

15. lépés: PWM modul felépítése- PWM funkció (I) csomagolása

Visszatérve a „helloworld.c” fő fájlhoz, tartalmazza a következő fejlécfájlokat:

16. lépés: PWM modul felépítése- PWM funkció (II) csomagolása

Határozza meg két AXI TImer báziscímét az „xparameters.h” segítségével.

17. lépés: PWM-modul felépítése- PWM-funkció (III) csomagolása

Készítse el a kívánt PWM funkciót.

Duty_val: a fokértéket munkaciklusmá alakítja át. Az óra időtartamát is hozzá kell rendelni.

PWM_START: rendelje hozzá a PWM regisztercímet, és indítsa el a PWM létrehozását.

PWM_STOP: rendelje hozzá a PWM regisztercímet, és állítsa le a PWM generálását.

A többi demókód a „helloworld.c” alatt jelenik meg az „Axis_2_PWM_SDK” alatt

18. lépés: PWM modul építése- futtassa

1. Programozza az FPGA -t SDK -n keresztül

- Csatlakoztassa a Zybo Boardot USB porton keresztül a számítógéphez.

- Xilinx Eszközök -> FPGA programozása

2. Futtassa a programot

Kattintson a „Futtatás” ikonra, és válassza ki a menüt -> Futtatás másként -> Indítás a hardveren

3. SDK terminál

- Nyissa meg az SDK terminált -> Csatlakozás soros porthoz -> OK

- Futtassa a programot. Ha a demókód sikeresen fut, akkor az „Inicializálás kész!” Üzenetet kell látnia. az SDK terminálon.

19. lépés: Streaming Video Processing on Digilent ZYBO with OV7670

Teljes archív fájl csatolva.

20. lépés: Töltse ki a blokkdiagramot

Ez a projekt összes kapcsolatának és IP -blokkjának teljes diagramját mutatja

21. lépés: Csatlakoztassa az OV7670 -et a ZYBO -hoz

Hozzon létre egy kapcsolatot az ov7670 modul ZYBO Pmod -okhoz való csatlakoztatásához

A Pmod adatok Pmod D

A Pmod vezérlőelem a Pmod C

Ezenkívül csatlakoztassa a PmodCON3 -at és a szervókat az oktatóanyag első felében leírtak szerint

22. lépés: Blokktervezés létrehozása

A Flow Navigatorban kattintson a "Blokkterv létrehozása" gombra, majd nyomja meg az OK gombot.

23. lépés: VHDL -fájlok hozzáadása az OV7670 kameravezérléshez és rögzítéshez

Adja hozzá a projekthez az ehhez a lépéshez csatolt VHDL fájlokat

24. lépés: Kényszerfájl hozzáadása

Adja hozzá a csatolt kényszerfájlt a projekthez.

25. lépés: IP -repó hozzáadása a HLS IP -hez

Vegye ki a csatolt Zip fájlt, és bontsa ki egy új mappába, amelyet hasonló módon neveznek el egy "HLS_repo" nevű új könyvtárban (mappában).

Adjon hozzá egy IP-lerakatot a projekthez az IP-katalógusban, és kattintson a jobb gombbal az „Adattár hozzáadása…” elemre.

Keresse meg a "HLS_repo" könyvtárat, és válassza ki.

Választható: HLS videófeldolgozó blokkot hozhat létre magának!

26. lépés: Modulok és IP hozzáadása

Adja hozzá az ov7670_axi_stream_capture, debounce és ov7670_controller modulokat a tömbdiagramhoz a jobb egérgombbal a háttérre kattintva, és válassza a "Modul hozzáadása …" lehetőséget.

Hasonlóképpen adja hozzá az IP -címeket:

- HLS_Video_Track

- Videókeretpuffer írás

- Videókeretpuffer olvasása

- Videó időzítő vezérlő

- AXI4-Stream videó kimenetre

- "Szelet" 3. része

- Állandó

- Az AXI időzítő 2

27. lépés: IP -konfigurációs beállítások

Ahogy a képeken is látható

28. lépés: A PS IP -blokk hozzáadása és konfigurálása

Adja hozzá a ZYNQ7 feldolgozó rendszert a tömbvázlathoz

szerkeszteni a konfigurációt:

-

PS-PL konfiguráció

-

HP

- Engedélyezze az S HP 0 -t

- Az S HP 1 engedélyezése

-

-

Óra konfiguráció

-

PL Szövet órák

- FCLK_0 100 MHz -en

- FCLK_1 25 MHz -en (kimeneti óra)

- FLCK_2 35 MHz -en (<= 50 MHz) (CameraClock)

-

29. lépés: 1. rész: PWM modul építése szervomotorokhoz

Hozza ki az axi_timer_0 pwm0 parancsot a pwm_Xaxis új kimeneti portba

Hozza ki az axi_timer_1 pwm0 parancsot a pwm_Zaxis új kimeneti portra

30. lépés: Videó bemeneti oldali csatlakozók (kiemelve)

Csatlakoztassa megfelelően a videó bemeneti oldali IP -blokkokat

(* ezeket a kapcsolatokat a megfelelő lehetőségek kiválasztásával kell létrehozni a kapcsolat automatizálása során) Az "aclk" az axi_stream_capture -ből a következő címre megy:

- ap_clk a videó keret puffer írásakor

- ap_clk a HLS videófolyam feldolgozási blokkján

- *Aclk az AXI smartconnect IP -n a Video Frame Bufferből Írjon az S_AXI_HP0 -ra

- *Aclk, amely megfelel az AXI Interconnect IP csatornáinak a HLS videófeldolgozó blokk S_AXI csatornáihoz és a videó keret pufferhez, írja az S_AXI_HP0_ACLK elemet a PS blokkra

A videófolyam jelét egyszerűen sorba kell kötni a rögzítési blokktól a Zynq memória interfészig.

- A videó a rögzítési blokkból a HLS feldolgozási blokkba kerül.

- A HLS blokkból feldolgozott videó a keretpuffer írási blokkjába kerül.

- *A keretpuffer írási blokk a Zynq PS blokk HP0 interfészéhez csatlakozik.

- A rögzítési blokk kimenetéről származó m_axis_tuser jel manuálisan van kötve mind a HLS feldolgozó blokk video_in_TUSER bemeneti jeléhez, mind az ap_start jelhez ugyanazon a blokkon.

A TUSER (tuser) jelet az AXI video stream protokoll használja a videó képkockájának kezdetének jelzésére. Az AP_Start jelzi a HLS blokknak, hogy kezdje meg a feldolgozást. Így tuser segítségével indítjuk el a HLS blokkot az egyes képkockák feldolgozásához. Ha egy busz egyetlen jelét csatlakoztatja, és ilyen módon lebontja, akkor a busz többi részének normál végpontját is csatlakoztatnia kell. Vivado feltételezi, hogy ha manuálisan csatlakoztatja a jelet, akkor le szeretné választani azt, amelyhez általában csatlakozik.

Az IP -blokkok konfigurációs beállításai:

Videókeret puffer írása:

Videó formátumok: RGB8

Óránként 1 minta Max. Oszlopok: 1280 (> = 640) Maximális sorok: 960 (> = 480) Max. Adatszélesség: 8

31. lépés: Csatlakozások az OV7670 -hez

Az ov7670_axi_stream_capture blokkon

- Tegye az összes bemenetet külsővé (kattintson jobb gombbal egy tűre, és válassza ki a menüből, vagy kattintson bal egérgombbal-> ctrl+T)

- Hagyja a neveket úgy, ahogy vannak

Az ov7670_controller blokkon

- Az összes blokk kimenetét tegye külsővé

- Nevezze át a config_finished portot led0 -ra

- csatlakoztassa a clk -t a CameraClock -hoz (<= 50MHz) (FCLK_2)

A visszakapcsolási blokkon

- csatlakoztassa a button1 bemenetet a btn0 nevű külső bemeneti porthoz

- csatlakoztassa az out1 -et az ov7670_controller IP -blokk újraküldési vonalához

- csatlakoztassa a button2 bemenetet a btn3 nevű külső bemeneti porthoz

- csatlakoztassa az out2n -t az ext_reset_in bemenethez a Processor System Reset IP -n a videó rögzítési óra tartományhoz. (*Lehet, hogy ezt meg kell tenni az IP létrehozása után*)

- csatlakoztassa a clk -t a CameraClock -hoz (<= 50MHz) (FCLK_2)

32. lépés: Csatlakozások a videó kimeneti oldalon

Csatlakozások blokkokhoz Video Timing Controller (VTC), AXI4-Stream to Video Out és szeletek

- Használjon 25 MHz -es órát (FCLK_1) a vid_io_out_clk és a VTC clk esetében

- Használjon 100 MHz-es órát (FCLK_0) az AXI4-Stream Video Out kimenethez

- vtiming_out to vtiming_in

- Videókeretpuffer Olvasás m_axis_video megy az AXI4-Stream to Video Out video_in

- vtg_ce megy gen_clken

- Kapcsolja össze a VTC -t clc, aclken, vid_io_out_ce a Constant Dout -nal [0: 0]

- Vigye ki a vid_hsync és a vid_vsync programokat a vga_hs és a vga_vs külső kimeneti portokra. (nincs a képen)

Szelet:

-

A szeleteket a mellékelt képek szerint kell beállítani

- nevezze át a blokkokat szelet_vörös, szelet_zöld és szelet_kék színűre

- beállítási szelet tartományok, ahogyan a képeken látható a blokk neve szerint

- Csatlakoztassa az egyes szeletkimeneteket egy külső port kimenethez, amint az a képen látható.

- A vid_data [23: 0] minden szelet bemenetéhez csatlakozik (Din [23: 0])

33. lépés: Futtassa a blokkolás és a kapcsolat automatizálását

Futtassa a Block Automation alkalmazást, hogy összekapcsolja a ZYNQ7 PS blokkból származó dolgokat. A képen látható módon.

Futtassa a kapcsolat automatizálását az összes összekapcsolási IP létrehozásához. Figyeljen minden lehetőségre minden képen.

A visszakapcsolási blokkon csatlakoztassa az out2n -t a videofelvételi óra tartományához Processor System Reset ext_reset_in bemenethez.

34. lépés: Hozzon létre HDL csomagolót

Hozza létre a HDL csomagolót a blokk kialakításához.

Állítsa be felső modulként.

35. lépés: Bitfolyam létrehozása, hardver exportálása SDK -ba, SDK indítása a Vivado -ból

Ügyeljen arra, hogy a bitfolyamot is exportálja.

A bitfolyam generálása nagyon sokáig tarthat.

Ezután indítsa el az SDK -t

36. lépés: SDK (nincs FreeRTOS)

Ez a verzió mindent megtesz a FreeRTOS használata nélkül, szépen sűrítve a kódot.

Hozzon létre önálló BSP -t a hardver kialakítása alapján. Az alapértelmezett beállításoknak rendben kell lenniük. Győződjön meg arról, hogy a BSP források létrejöttek.

Alkalmazás létrehozása a képen látható módon. (üres alkalmazás)

Törölje az automatikusan generált főt, és importálja a csatolt fájlokat.

37. lépés: FreeRTOS implementáció

Ez a verzió a FreeRTOS -t használja. Hozzon létre egy FreeRTOS901 BSP -t a hardver kialakítása alapján. Az alapértelmezett beállításoknak rendben kell lenniük. Győződjön meg arról, hogy a BSP források létrejöttek.

Alkalmazás létrehozása a képen látható módon. (üres alkalmazás)

Törölje az automatikusan generált főt, és importálja a csatolt fájlokat.

38. lépés: Használati utasítások

Ez a projekt egy kicsit bonyolult elindulni. Kövesse a lépéseket sorrendben.

Győződjön meg arról, hogy a ZYBO nem tölt be semmit, amikor bekapcsol. Ez azt jelenti, hogy a Kész LED -nek nem szabad világítania. Ennek egyik módja a rendszerindító forrás jumper beállítása JTAG -ra.

Nyissa meg azt a projektet (FreeRTOS vagy sem), amelyet SDK -ból szeretne programozni

- Kapcsolja be a ZYBO -t. A Kész LED -nek nem szabad világítania.

- Programozza az FPGA -t a bit fájllal. A Kész LED -nek világítania kell. A Led0 nem világíthat.

- Futtassa a kódot (ne felejtse el elmenni a kezdő töréspont mellett, ha ezt teszi).

Ezen a ponton egy kimenetet kell kapnia a VGA kijelzőjén.

Az újraindítás (ha hibás vagy bármi más): gyorsan érintse meg a PS-SRST gombot, vagy kapcsolja ki, majd újra a ZYBO-t. Folytassa a 2. lépéssel.

Ha leállítja a processzort a hibakeresővel, a fényképezőgép mozdulatlan helyzetben marad. A videófolyam mindenesetre folytatódik.

39. lépés: Hivatkozások és hivatkozások

Xilinx referencia útmutatók és dokumentáció:

- PG044 - AXI -Stream videó kimenetre

- PG278 - Videókeretpuffer olvasás/írás

Egyéb linkek:

- Lauri blogja - VDMA bemenet

- Lauri blogja - OV7670 - VGA kimenet BRAM használatával

- Hamsterworks wiki, Mike Fields, az OV7670 kód eredeti forrása

- Adatlap, amely az alapvető időzítési előírásokat mutatja

Ajánlott:

Végső szárazjég -ködgép - Bluetooth -vezérléssel, elemmel és 3D nyomtatással: 22 lépés (képekkel)

Végső szárazjég -ködgép - Bluetooth -vezérelt, elemmel működtetett és 3D nyomtatással .: Nemrég szükségem volt egy szárazjéggépre, hogy néhány színházi effektust kapjak egy helyi bemutatóhoz. A költségvetésünk nem terjedne el arra, hogy felvegyünk egy professzionális munkatársat, ezért ezt építettem helyette. Többnyire 3D nyomtatott, távolról vezérelhető bluetooth -on keresztül, akkumulátoros energiával

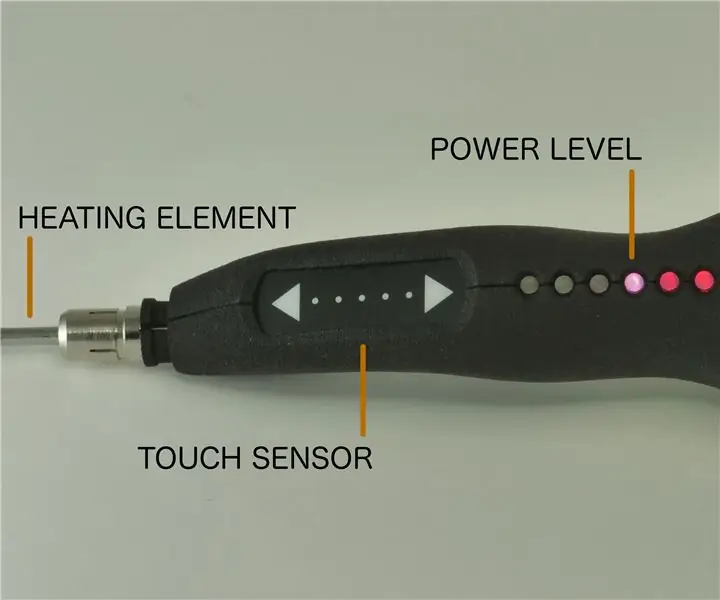

Solderdoodle Plus: Forrasztópáka érintőképernyős vezérléssel, LED visszajelzéssel, 3D nyomtatott tokkal és újratölthető USB -vel: 5 lépés (képekkel)

Solderdoodle Plus: Forrasztópáka érintőképernyős vezérléssel, LED visszajelzéssel, 3D nyomtatott tokkal és újratölthető USB-vel: Kattintson az alábbi linkre, hogy meglátogassa a Kickstarter projektoldalunkat a Solderdoodle Plus, egy vezeték nélküli USB újratölthető forró multifunkciós szerszámhoz, és előrendelje a gyártási modellt! Https: //www.kickstarter.com/projects/249225636/solderdoodle-plus-cordless-usb-rechargeable-ho

CAR-INO: Egy régi RC autó teljes átalakítása Arduino és Bluetooth vezérléssel: 5 lépés (képekkel)

CAR-INO: Egy régi RC autó teljes átalakítása Arduino-val és Bluetooth-vezérléssel: Bevezetés Szia, az első oktatási anyagomban szeretném megosztani veled tapasztalataimat egy régi rc autó 1990-es évről újra történő átalakításáról. Karácsony volt 1990, amikor a Mikulás nekem adta ezt a Ferrari F40 -et, a világ leggyorsabb autóját! … akkoriban. T

IOT123 - SOLAR TRACKER - TILT/PAN, PANEL FRAME, LDR MOUNTS RIG: 9 lépés (képekkel)

IOT123 - SOLAR TRACKER - TILT/PAN, PANEL FRAME, LDR MOUNTS RIG: A legtöbb DIY tervezés kéttengelyes napelemes nyomkövetőkhöz " odakinn " a 9G Micro Servo-n alapulnak, amelyek valóban alulértékeltek, hogy néhány napelemet, a mikrovezérlőt, az akkumulátort és a házat körbejárják. Körülbelül tervezhet

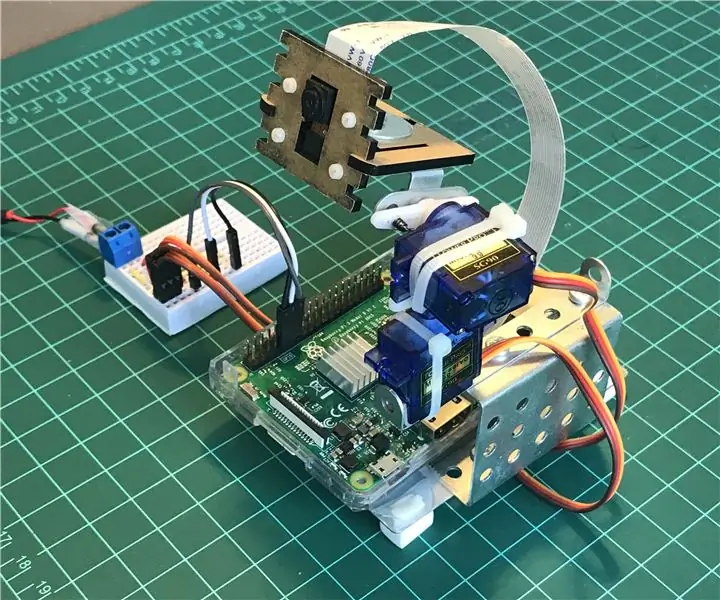

Pan-Tilt Multi Servo Control: 11 lépés (képekkel)

Pan-Tilt Multi Servo Control: Ebben az oktatóanyagban megvizsgáljuk, hogyan lehet több szervót vezérelni a Python használatával egy Raspberry Pi-n. Célunk egy PAN/TILT mechanizmus lesz egy kamera elhelyezésére (PiCam). Itt láthatja, hogyan fog működni a végső projektünk: Control Servo Control hurok teszt: