Tartalomjegyzék:

- Szerző John Day day@howwhatproduce.com.

- Public 2024-01-30 09:41.

- Utoljára módosítva 2025-01-23 14:47.

Korábbi utasításomban láttuk, hogyan kell megtervezni egy egyszerű közvetlen leképezett gyorsítótár -vezérlőt. Ezúttal egy lépéssel előre lépünk. Egy egyszerű négyirányú asszociatív gyorsítótár-vezérlőt tervezünk. Előny? Kevesebb kihagyási arány, de a teljesítmény árán. Csakúgy, mint az előző blogom, egy teljes processzort, fő memóriát és gyorsítótár -környezetet tervezünk és emulálunk a gyorsítótár -vezérlő teszteléséhez. Remélem, srácok ezt hasznos referenciaként fogják fel a fogalmak megértéséhez és a saját gyorsítótár -vezérlők megtervezéséhez a jövőben. Mivel a processzor (tesztpad) modellje és a fő memóriarendszer pontosan megegyezik az előző blogommal, nem fogom újra elmagyarázni őket. Kérjük, olvassa el az előző utasításban a részleteket ezzel kapcsolatban.

1. lépés: Specifikációk

Gyors áttekintés az itt bemutatott gyorsítótár -vezérlő specifikációiban:

- Négyirányú asszociatív gyorsítótár-vezérlő (kattintson erre a linkre, ha közvetlen leképezett gyorsítótár-vezérlőt keres).

- Egy bankos, blokkoló gyorsítótár.

- Írási találatok írási irányelvei.

- Írási kör szabályok az írási hibákról.

- A fa ál-LRU (pLRU) cserepolitikája.

- Tag Array a vezérlőn belül.

- Konfigurálható paraméterek.

A gyorsítótár -memória és a fő memória alapértelmezett adatai megegyeznek az előző utasításommal. Kérjük, hivatkozzon rájuk.

2. lépés: A teljes rendszer RTL nézete

A felső modul teljes RTL -ábrázolása az ábrán látható (a processzor kivételével). A buszok alapértelmezett paraméterei a következők:

- Minden adatbusz 32 bites busz.

- Címbusz = 32 bites busz (de a memória itt csak 10 bitet címezhet).

- Adatblokk = 128 bit (széles sávszélességű busz olvasáshoz).

- Minden alkatrészt ugyanaz az óra hajt.

3. lépés: Vizsgálati eredmények

A felső modult egy tesztpad segítségével tesztelték, amely egyszerűen egy nem csővezetékes processzort modellez, ugyanúgy, mint az utolsó utasításban. A tesztpad gyakran generál olvasási/írási kéréseket a memóriába. Ez csúfolja a tipikus "Load" és "Store" utasításokat, amelyek minden processzor által végrehajtott programban gyakoriak.

A teszteredmények sikeresen ellenőrizték a Cache Controller működését. Az alábbiakban a vizsgált statisztikák láthatók:

- Minden olvasási/írási hiányzó és találati jel helyesen lett generálva.

- Az összes olvasási/írási művelet mind a négy módon sikeres volt.

- A pLRU algoritmus sikeresen ellenőrizve van a gyorsítótár sorainak cseréjéhez.

- Nem észleltek adatkonkoherencia/következetlenségi problémákat.

- A tervezést sikeresen ellenőrizték a Maxm -hez. Óra Működési frekvencia = 100 MHz Xilinx Virtex-4 ML-403 kártyán (teljes rendszer), 110 MHz csak a gyorsítótár-vezérlőnél.

- A blokk -RAM -okat a fő memóriára következtették. Az összes többi tömb LUT -on valósult meg.

4. lépés: Csatolt fájlok

Ehhez a bloghoz a következő fájlok vannak csatolva:

- . HD fájlok a Cache Controller, Cache Data Array, Main Memory System.

- Próbapad.

- Dokumentáció a Cache Controllerről.

Megjegyzések:

- Olvassa el a dokumentációt, hogy teljes mértékben megértse az itt bemutatott gyorsítótár -vezérlő specifikációit.

- A kód bármilyen módosítása más moduloktól függ. Tehát a változtatásokat megfontoltan kell végrehajtani.

- Figyeljen az összes megjegyzésre és fejlécre, amelyeket adtam.

- Ha valamilyen oknál fogva a blokk -RAM -ok nem következtetnek a fő memóriára, CSÖKKENTJE a memória méretét, majd a címsín szélességének változása a fájlokban és így tovább. Így ugyanaz a memória megvalósítható akár LUT -okon, akár elosztott RAM -on. Ez időt és erőforrásokat takarít meg. Vagy keresse fel az adott FPGA dokumentációt, és keresse meg a kompatibilis kódot a RAM blokkolásához, és ennek megfelelően szerkessze a kódot, és használja ugyanazokat a címbusz -szélességi előírásokat. Ugyanez a technika az Altera FPGA -knál.

Ajánlott:

Mobil vezérelt Bluetooth autó -- Egyszerű -- Egyszerű -- Hc-05 -- Motorpajzs: 10 lépés (képekkel)

Mobil vezérelt Bluetooth autó || Egyszerű || Egyszerű || Hc-05 || Motorpajzs: … Kérem, Iratkozzon fel YouTube-csatornámra ………. Ez a Bluetooth-vezérlésű autó, amely HC-05 Bluetooth modult használt a mobiltelefonnal való kommunikációhoz. Bluetooth -on keresztül irányíthatjuk az autót mobiltelefonnal. Van egy alkalmazás az autó mozgásának szabályozására

Egyszerű és egyszerű Pókember Web-Shooter: 12 lépés

Egyszerű és egyszerű Pókember Web-Shooter: Láttál Pókember-filmet? Pókember-képregény? Bármi, ami homályosan Pókemberhez kapcsolódik? A Pókember látszólag mindenhol ott van. Miért nem készít egy egyszerű web-shooter-t? Kis gyakorlás után a ház anyagaiból létrehoztam egy dizájnt, amely létrehozható

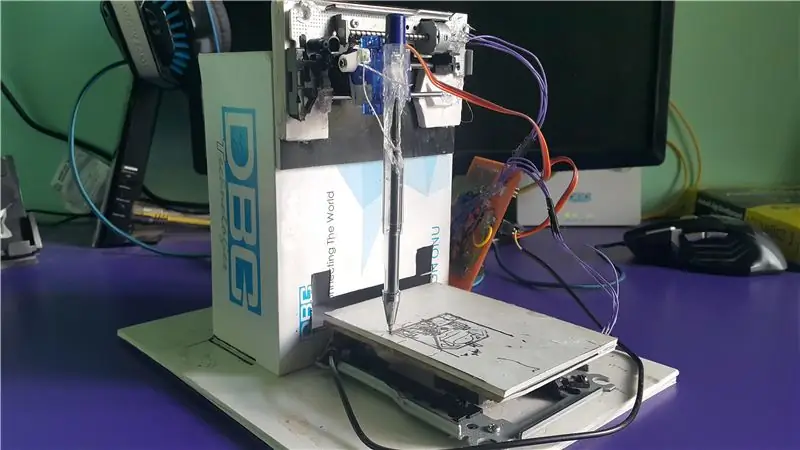

Egyszerű, egyszerű házi feladatgép: 4 lépés (képekkel)

Egyszerű, egyszerű házi feladat: Ez a gép olcsó anyagokból készült, és nem haladja meg a 7 dollárt. Ennek felépítéséhez türelemre és 2 órára van szüksége. És ismernie kell a forrasztást és a huzalozást, mivel ez kis áramkört foglal magában. Ha megépült, csak csatlakoztassa

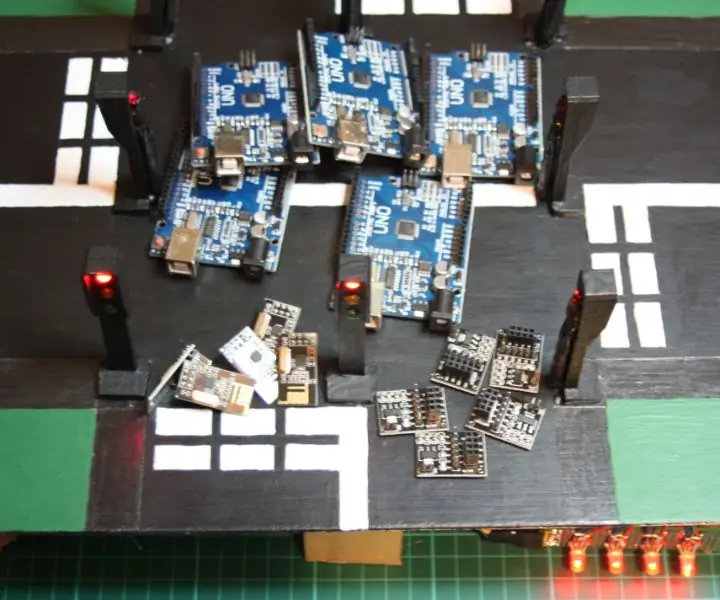

Négyirányú közlekedési lámparendszer 5 Arduino és 5 NRF24L01 vezeték nélküli modul használatával: 7 lépés (képekkel)

Négyirányú jelzőlámpa -rendszer 5 Arduino és 5 NRF24L01 vezeték nélküli modul használatával: Nem sokkal ezelőtt létrehoztam egy Instructable -t, amely részletesen leírja az egyetlen pár jelzőlámpát egy kenyérsütő táblán. Létrehoztam egy másik Instructable -t is, amely bemutatja az NRF24L01 vezeték nélküli modul használatának alapvető keretét. elgondolkodtam! Nagyon sok van

LED sakk készlet - egyszerű verzió: 12 lépés

LED sakk készlet-egyszerű verzió: A Tetranitrate korábban kitűnő útmutatást tett közzé arról, hogyan készítsen egy LED sakkkészletet: https: //www.instructables.com/id/LED-Chess-Set/ t ne zavarjon, ha oly villanónak tűnő képet készít. Csak egyet akartam