Tartalomjegyzék:

- 1. lépés: Blokkdiagram

- 2. lépés: Működési elv

- 3. lépés: Logikai megvalósítás

- 4. lépés: A patthelyzet megoldása

- 5. lépés: Eszközkonfiguráció - Mátrix0 áramkör

- 6. lépés: Eszközkonfiguráció - SPI Clocking Logic

- 7. lépés: Eszközkonfiguráció - Mátrix0 -összetevők tulajdonságai

- 8. lépés: Eszközkonfiguráció - Mátrix1 áramkör

- 9. lépés: Eszközkonfiguráció - 3 bites bináris számláló

- 10. lépés: Eszközkonfiguráció - 3 bites összehasonlítási logika

- 11. lépés: Eszközkonfiguráció - Logikai és ideiglenes nyilvántartás digitális összehasonlítása

- 12. lépés: Eszközkonfiguráció - Mátrix1 összetevők tulajdonságai

- 13. lépés: Eredmények

- Szerző John Day day@howwhatproduce.com.

- Public 2024-01-30 09:40.

- Utoljára módosítva 2025-01-23 14:47.

A vezérlőrendszerek és a kapcsolódó eszközök több áramforrással, például előfeszítő vonallal vagy akkumulátorral foglalkoznak, és követniük kell a legmagasabb (vagy legalacsonyabb) vonalat egy adott halmaz között.

Például a „több akkumulátoros” rendszerben a terhelésváltás megköveteli, hogy a rendszer figyelje az akkumulátor tömb minimális vagy maximális feszültségét (max vagy min az adott kapcsolási algoritmus függvényében), és dinamikusan irányítsa a terhelést a a legmegfelelőbb forrás valós időben. Alternatív megoldásként előfordulhat, hogy a rendszernek ideiglenesen le kell választania a legalacsonyabb feszültségű akkumulátort a megfelelő töltés érdekében.

Egy másik példa a korszerű napenergia -rendszer, ahol minden napelem elforgatható mechanizmussal és szolárkövető áramkörrel van felszerelve (ez utóbbi szolgáltatja a Nap helyzetére vonatkozó információkat a panel tájékozódásához). A maximális feszültség információval minden szolárpanel pozíciója finomhangolható a húr panel alapján, amely ténylegesen a legnagyobb kimeneti feszültséget biztosítja, ezáltal kiváló teljesítményoptimalizálást érve el.

A kereskedelmi IC -k több különböző márkája létezik (főleg mikrokontrollerek), amelyek elvileg képesek maximális feszültségkövetőt megvalósítani. Ezek azonban programozást igényelnek, és kevésbé költséghatékonyak, mint a vegyes jelű megoldások. A Dialog GreenPAKTM tervezésének kiegészítése pozitívan befolyásolhatja a design megfizethetőségét, méretét és modularitását. Ez a kialakítás kihasználja annak az előnyét, hogy az analóg és a digitális áramkört egyetlen chipbe integrálja.

Ebben az utasításban az analóg kezelőfelület és a digitális logika szükséges a maximális (vagy végül min) feszültségkereső megvalósításához nyolc különböző forrás között.

A 8 csatornás analóg max/min feszültségfigyelő megvalósításához SLG46620G-t használnak.

Az alábbiakban ismertettük a szükséges lépéseket annak megértéséhez, hogy a megoldás hogyan lett programozva a 8 csatornás analóg max/min feszültségfigyelő létrehozásához. Ha azonban csak a programozás eredményét szeretné elérni, töltse le a GreenPAK szoftvert a már elkészült GreenPAK tervezési fájl megtekintéséhez. Csatlakoztassa a GreenPAK fejlesztőkészletet a számítógépéhez, és nyomja meg a programot a 8 csatornás analóg max/min feszültségfigyelő létrehozásához.

1. lépés: Blokkdiagram

Az 1. ábra a megvalósított rendszer globális diagramját mutatja.

Egy legfeljebb 8 változó feszültségű forrásból álló karakterlánc multiplexelhető és kapcsolódik a GreenPAK ADC moduljához, amely egy személyre szabott belső kialakításhoz van csatlakoztatva, amely képes a többi feszültséghez képest a legnagyobb feszültségű forrás kiválasztására. A belső logika megjeleníti ezeket az információkat megjelenítés vagy további feldolgozás céljából.

A tervezés a GreenPAK SLG46620G terméken alapul, mivel az alkalmazáshoz szükséges analóg és digitális építőelemeket tartalmazza. Ebben a megvalósításban a tömb egy ADG508 analóg multiplexer segítségével kerül szkennelésre, amelyet közvetlenül a GreenPAK IC hajt.

A kimeneti információ egy 3 bites digitális szám, amely megfelel a feszültségforrás számának a maximális feszültségnél. Ennek az információnak a közvetlen módja a szám megjelenítése egy 7 szegmenses kijelzőn. Könnyen megvalósítható, ha az SLG46620G digitális kimenetét egy 7 szegmenses kijelző-illesztőprogramhoz csatlakoztatja, például a Hivatkozásban leírt GreenPAK megoldáshoz vagy egy közös 74LS47 IC-hez.

A bemutatott áramkör a maximális feszültséget keresi. Ahhoz, hogy a kialakítást minimális feszültségkeresővé alakítsák, egyszerű előkondicionáló áramkört kell hozzáadni az analóg multiplexer és a GreenPAK analóg bemenet közé, levonva a multiplexer kimenetét az 1 V-os referenciafeszültségről.

2. lépés: Működési elv

A tervezés célja a maximális feszültségű forrás kiválasztása, ezért a szkennelés a teljes tömbön történik, miközben tárolja az utolsó-max értéket, és összehasonlítja azt a bemenet következő értékével (amely a vizsgálat következő feszültségforrásához tartozik).

A következőkben egy teljes multiplexelési szekvenciára hivatkozunk az összes bemenet mentén, mint „szkennelés” vagy „hurok”.

A két érték összehasonlítását nem az ACMP komponensek segítségével lehet elvégezni (amelyek az SLG46620G -ben kaphatók), hanem inkább a DCMP modul segítségével, miután az értékeket digitalizálják. Ez egy fejlett és kifinomult technika, amelyet először a Reference tartalmaz.

A 2. ábra azt mutatja, hogy az SLG46620G hogyan épül fel ehhez a kialakításhoz.

Az analóg bemeneti jel az ADC bemenetre megy a PGA komponensen keresztül, 1-es erősítéssel. Különböző erősítési beállítások is lehetségesek, hogy megtalálják a legjobb illeszkedést az előlapi kondicionáló elektronikával, amely a bemeneti feszültségek 0-1 V-ra való leképezésére szolgál. a GreenPAK ADC modul tartományát.

Az ADC egyvégű üzemmódban működik, és az analóg jelet 8 bites digitális kódgá alakítja, amelyet ezután továbbít a DCMP modulba. A digitális kód bekerül az SPI blokkba is, amely ADC/FSM pufferként van konfigurálva, ahol a digitális kód tárolható, és nem változik, amíg a következő impulzus el nem érkezik az SPI CLK bemenetre. Vegye figyelembe, hogy egy dedikált logikai blokk hajtja az SPI CLK bemenetet. Ezt a részt később megvizsgáljuk, mivel ez az „alapvető” logika, amely felelős a megfelelő működésért. Az új digitális kód csak akkor kerül tárolásra az SPI modulban, ha az a tényleges maximális bemeneti feszültséghez tartozik.

A DCMP komponens az aktuális ADC adatok összehasonlítására szolgál az SPI blokkban tárolt utolsó nyertessel (azaz az utolsó talált értékkel). Impulzust generál az OUT+ kimeneten, ha az új ADC adatok nagyobbak, mint az előzőek. Az OUT+ jel használatával frissítjük az SPI blokkot az új nyertessel.

A globális órajel vezérli az ADC konverziókat és az általános időzítéseket. A konverzió végrehajtása után az ADC INT kimeneti jele impulzusokat küld, időben koordinálva az ADC párhuzamos adatkimenettel. Az INT kimenetet használjuk a 3 bites bináris számláló növelésére is, amelyet a DFF-ek valósítanak meg a Matrix1-ben, ami három okból hasznos:

1. A számláló kimeneti vonalai a külső analóg multiplexert célozzák, így szolgálva az ADC következő bemeneti feszültségét;

2. A számlálót egy 3 bites regiszterbe fagyasztják (a Matrix1-ben implementálva), hogy tárolja az ideiglenes nyertest a vizsgálat során;

3. A számláló dekódolva frissíti a második 3 bites regisztert (a Matrix0-ban van megvalósítva), miután a vizsgálat befejeződött.

3. lépés: Logikai megvalósítás

Az ADC modul sorban, végtelenségig biztosítja az összes bemeneti feszültség konvertált adatait. Miután a multiplexer címzettje 0b111 (decimális 7), a számláló 0b000 -re (decimális 0) gördül le, és ezáltal megkezdi a bemeneti feszültségek új vizsgálatát.

A szkennelés során az ADC INT kimeneti jel generálódik, ha a párhuzamos adatkimenet érvényes. Amikor ez a jel pulzál, az analóg multiplexernek át kell kapcsolnia a következő bemenetre, biztosítva a PGA -nak a megfelelő feszültséget. Ezért az ADC INT kimenet a 2. ábra 3 bites bináris számlálójának közvetlen órajele, amelynek 3 bites párhuzamos kimeneti szava közvetlenül a külső analóg multiplexerhez szól („V select” az 1. ábrán).

Nézzünk most egy példát, ahol a bemeneti feszültségeknek a következő összefüggésekkel kell rendelkezniük:

a) V0 <V1 <V2

b) V2> V3, V4

c) V5> V2

A 3. ábra a max-döntési mechanizmus főbb jeleit mutatja be.

Mivel az adatok végül az INT impulzusokkal szinkronban kerülnek az SPI pufferregiszterbe, létezik egy összehasonlító ablak, ahol az SPI puffer tartalmát összehasonlítják a következő ADC konverziós eredménnyel. Ez az időzítés OUT+ impulzusok generálását eredményezi a DCMP kimeneten. Ezeket az impulzusokat kihasználva új értékeket tölthetünk be az SPI pufferregiszterbe.

Amint az az előző ábrán látható SPI puffer adatsorból kitűnik, az SPI regiszter mindig tartalmazza időről időre a legnagyobb értéket a 8 bemenet között, és csak akkor frissül, ha a DCMP modul nagyobb értéket észlel (hivatkozva a DCMP -re) A diagram OUT+ kimeneti vonala, a hiányzó impulzusok miatt a V2 reteszelve marad a regiszterben mindaddig, amíg a V5).

4. lépés: A patthelyzet megoldása

Ha a megvalósított logika a fent leírtak szerint lenne, akkor egyértelmű, hogy holtpontra kerülünk: a rendszer csak az SPI pufferregiszterben tárolt feszültségnél magasabb feszültségeket képes észlelni.

Ez abban az esetben is érvényes, ha ez a feszültség csökkenne, és akkor egy másik bemenet, amely ennél alacsonyabb, a legmagasabb lesz: soha nem észlelhető. Ezt a helyzetet jobban megmagyarázza a 4. ábra, ahol csak 3 bemeneti feszültség van jelen világosság.

A 2. iteráció idején a V3 csökken, és V1 a tényleges maximális feszültség. De a DCMP modul nem ad impulzust, mert az SPI pufferregiszterben tárolt adatok (megfelelnek 0,6 V -nak) nagyobbak, mint a V1 (0,4 V).

A rendszer ekkor „abszolút” max keresőként viselkedik, és nem frissíti megfelelően a kimenetet.

Szép módja ennek a problémának a kiküszöbölésére az adatok kényszerített újratöltése az SPI pufferregiszterbe, amikor a rendszer befejezi az összes csatorna teljes lekérdezési ciklusát.

Valójában, ha az adott bemeneten a feszültség még mindig a legmagasabb, semmi sem változik, és a vezérlés biztonságosan folytatódik (lásd a fenti 4. ábrát, ez a 0. és 1. hurok -ismétlés esete). Másrészt, ha az adott bemeneten lévő feszültség véletlenül lecsökken egy másik bemenetnél kisebb értékre, akkor az érték újratöltése lehetővé teszi a DCMP modul számára, hogy OUT+ impulzust állítson elő, amikor összehasonlítja az új maximális értékkel (ez a a 2. és 3. ciklus ismétlésének esete).

A probléma megoldásához szükség van egy logikai áramkörre. Órajelet kell generálnia az SPI komponensnek, amikor a ciklus eléri a tényleges maximális bemenetet, így kényszerítve a frissített adatszó újratöltését az SPI pufferregiszterbe. Ezt az alábbi 7.2. És 7.6. Szakasz tárgyalja.

5. lépés: Eszközkonfiguráció - Mátrix0 áramkör

Az SLG46620G két mátrixblokkal rendelkezik, amint azt a 2. ábra mutatja. A következő ábrák a megfelelő eszközkonfigurációkat mutatják be.

Az áramkör felső része a „Hurokregiszter”, amely 3 DFF -el (DFF0, DFF1 és DFF2) valósul meg. A bemeneti multiplexer minden ciklusa után frissül, hogy elküldi egy 7 szegmenses kijelző-illesztőprogramnak a „nyertes” bináris számát, vagyis azt a bemenetet, amely a legmagasabb feszültséggel rendelkezik az utolsó vizsgálat során. Mind a DFF -ek órája, mind az adatok a Matrix1 -ben megvalósított logikából származnak a P12, P13, P14 és P15 porton keresztül.

Az alsó rész az analóg előlap, a bemenet a 8. érintkezőn és a PGA x1 erősítéssel. Az ADC INT kimenet mind az SPI órajelző logikájához, mind a Matrix1 -hez megy a P0 porton keresztül, ahol az órajelként szolgál a megvalósított számlálóhoz.

Az ADC és SPI párhuzamos adatkimenetek NET11 és NET15 címkével vannak ellátva, hogy csatlakoztathatók legyenek a Matrix1 DCMP összetevőjéhez.

6. lépés: Eszközkonfiguráció - SPI Clocking Logic

Amint arra a „Logikai megvalósítás” részben korábban már utaltunk, az SPI pufferregiszter minden alkalommal frissül, amikor a tényleges tárolt érték és az új ADC konverziós adatok közötti összehasonlítás impulzust generál a DCMP OUT+ kimeneten.

A jel integritása akkor biztosított, ha ezt a jelet ÉS-ed az ADC INT kimenettel. Ezzel elkerülhetők a tüskék és a hamis indítások.

Azt is aláhúztuk, hogy a patthelyzetek kihagyásához az SPI -puffert frissíteni kell, amikor a ciklus eléri a tényleges nyertes adatokat.

Három jel van a játékban a megfelelő SPI -órajelzéshez:

1. ADC INT kimenet (LUT0-IN1)

2. DCMP OUT+ kimenet (LUT0-IN0 a P10 porton keresztül)

3. A szám megegyezik a retesz jelével (LUT0-IN2 a P11 porton keresztül)

Az első kettő ÉS-szerkesztésű, és mindkettő VAGY-szerű az utóbbival az LUT0-ban, amelynek megvalósítása a 6. ábra szerint van konfigurálva.

7. lépés: Eszközkonfiguráció - Mátrix0 -összetevők tulajdonságai

A 7-10. Ábrák a Matrix0-hoz tartozó többi komponens tulajdonságablakát mutatják be.

8. lépés: Eszközkonfiguráció - Mátrix1 áramkör

9. lépés: Eszközkonfiguráció - 3 bites bináris számláló

Az áramkör felső része logikai elemeket tartalmaz, főként egy 3 bites bináris számlálót, amelyet az ADC INT kimenet időzít, amint azt már tárgyaltuk. Ez a számláló a 12. ábrán látható "szabványos" sematikával van megvalósítva.

Ezt a számlálót tervezésünkben a DFF9, DFF10, DFF11 és INV1, LUT4, LUT8 papucsok segítségével valósítjuk meg. A DFF9 kimenet az LSB, míg a DFF11 az MSB, amint az a 13. ábrán látható.

Az LUT4 XOR-ként van konfigurálva, míg a LUT8 a 12. ábra AND-XOR logikáját hajtja végre.

A számláló kimenetek három digitális kimeneti érintkezőhöz mennek a külső analóg multiplexer címzéséhez.

A LUT10 dekódolja a számláló kódját, amikor a szkennelés befejeződött, és impulzust ad a Matrix0 -nak a DLY8 és a P12 porton keresztül. Ez egyszerűen a számláló kimeneteinek ÉS bekapcsolásával érhető el, így dekódolva a 7 dec számot (0b111 bináris, ciklus vége).

10. lépés: Eszközkonfiguráció - 3 bites összehasonlítási logika

A 15. ábra azt az áramkört mutatja, amelyet annak érzékelésére használnak, hogy a ciklus iterál az aktuális „nyertes” címen. Ebben az esetben, amint azt már említettük, a digitális impulzusnak kényszerítenie kell az aktuális ADC eredmény újratöltését az esetleges holtpont megoldása érdekében.

A „nyertes” cím a Matrix1 ideiglenes regiszterében tárolódik (lásd alább), míg az aktuális címet a bináris számláló adja ki.

Az XNOR kapuk valódi (logikai 1 vagy „magas”) kimenetet biztosítanak, ha mindkét bemenet egyenlő. ÉS ha ezt a jelet minden bitre (LUT9) adjuk, akkor impulzust kapunk, ha mindkét bináris kód azonos. A XOR kapukról, mint paritásellenőrzőről részletesen a Reference című részben olvashat.

A „Counter-equals-Latch” jelet a P11 porton keresztül továbbítják a Matrix0-nak.

11. lépés: Eszközkonfiguráció - Logikai és ideiglenes nyilvántartás digitális összehasonlítása

A 11. ábra alsó része (kiemelve a 16. ábrán) a DCMP blokkot, a tervezés döntési részét mutatja.

A DFF6, 7 és 8 3 bites regisztert képez, hogy tárolja az ideiglenes „nyertes” bemeneti számot, amíg a ciklus fut. A papucsok bemenetei a 3 bites bináris számláló kimenetek, amint az a 11. ábra globális Mátrix1 áramkörében látható, az áttekinthetőség kedvéért itt kihagyva.

Ennek a regiszternek a kimenetei nem tudják közvetlenül meghajtani a 7 szegmenses kijelzőt, mert az itt tárolt érték megváltozik a vizsgálat során, és csak a vizsgálat végén kell érvényesnek tekinteni.

Emiatt az ideiglenes regiszter kimenetek a P13, P14 és P15 mátrixközi portokon keresztül csatlakoznak a Matrix0 hurokregiszteréhez.

Fontos megfigyelni a 16. ábrán, hogy az ideiglenes regisztert a DCMP OUT+ kimenet órajelezi, amikor az ADC-SPI regiszterek összehasonlítása új maximális eredményt eredményez.

Ugyanezt az OUT+ jelet továbbítja a Matrix0, SPI CLK Logic a P10 porton keresztül.

12. lépés: Eszközkonfiguráció - Mátrix1 összetevők tulajdonságai

A 17-19. Ábrák a Matrix1-hez tartozó komponens tulajdonságablakokat mutatják be.

13. lépés: Eredmények

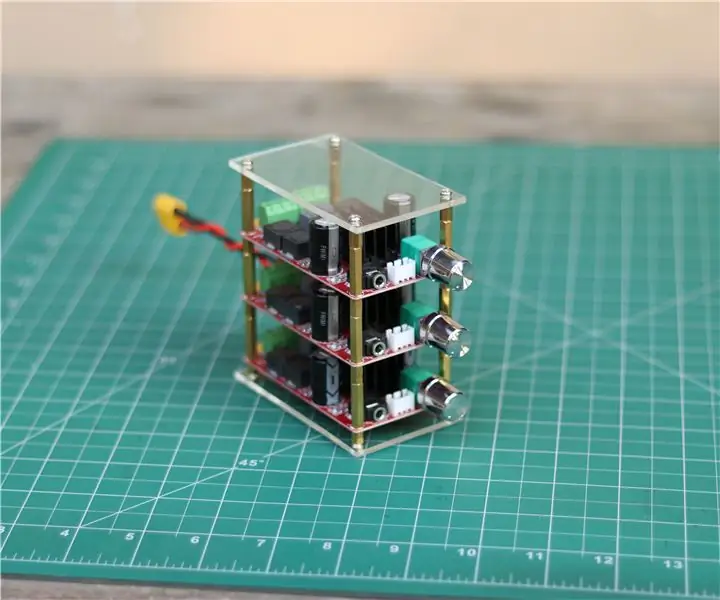

A megvalósítás teszteléséhez egy kiértékelő tábla prototípusát készítették el, ahol a 8 analóg bemeneti feszültséget egy sor ellenállásosztó adja meg TrimPots segítségével (amint az a 20. ábrán látható).

A használt multiplexer egy ADG508, amely egy tápellátással (12 V) működik.

A 7 szegmenses kijelző illesztőprogram egy 74LS47. Dekódolja a párhuzamos bemeneti szót, és közvetlenül meghajt egy közös anódos, 7 szegmenses kijelzőt.

Az értékelő tábla 2x10 derékszögű csatlakozóval rendelkezik, amely közvetlenül a GreenPAK Advanced Development Platformhoz csatlakoztatható annak bővítőcsatlakozójánál, amint az a 21. ábrán látható.

A GreenPAK Advanced Development Platform együttes használata nagyon egyszerűvé teszi a jelek mérését a gyors ellenőrzés érdekében. Például a 22. ábra a HP 54620A logikai elemző által rögzített jelek egy sorát mutatja (CLOCK, ADC INT kimenet és DCMP OUT+ kimenet). A hullámformákat az OUT+ jel emelkedő éle váltja ki (az „A> B” jelzésű skálán), ezért ez egy hullámforma rögzítés, amikor új maximális feszültséget észlel az analóg bemenetek között. Valójában azt az Értékelő Testület egyik TrimPotjának elforgatásával kaptuk, hogy növeljük a 22. ábrán látható megfelelő feszültséget.

A 23. ábra az Értékelő Testület vázlatát mutatja.

Következtetés

Ebben az utasításban egy nyolccsatornás max (vagy min) feszültségkeresőt valósítottunk meg, amelyet a többcsatornás vezérlőrendszerek közös kiegészítéseként használnak. A bemutatott megközelítés a GreenPAK komponensek fejlett tulajdonságait használja fel, és bemutatja, hogyan lehet integrálni egyetlen chipes analóg és digitális funkciókba. Számos kereskedelmi IC cserélhető Dialog GreenPAK -kkal, így csökkenthető az alkalmazás mérete és költsége.

Ajánlott:

Feszültségfigyelő nagyfeszültségű akkumulátorokhoz: 3 lépés (képekkel)

Feszültségfigyelő nagyfeszültségű akkumulátorokhoz: Ebben az útmutatóban elmagyarázom Önnek, hogyan építettem fel akkumulátorfeszültség -figyelőmet elektromos elektromos deszkámhoz. Szerelje fel, ahogy akarja, és csak két vezetéket csatlakoztasson az akkumulátorhoz (Gnd és Vcc). Ez az útmutató feltételezte, hogy az akkumulátor feszültsége meghaladja a 30 voltot

DIY 300 wattos 5.1 csatornás erősítő: 12 lépés (képekkel)

DIY 300 wattos 5.1 csatornás erősítő: Hé! mindenki A nevem Steve. Ma megmutatom, hogyan készítsünk 5.1 csatornás erősítőt Kattintson ide a videó megtekintéséhez Kezdjük

DIY 3 csatornás csúszógyűrű: 3 lépés

DIY 3 csatornás csúszógyűrű: Sziasztok! Ebben az oktatóanyagban bemutatom, hogyan készítsünk egy DIY 3 csatornás csúszógyűrűt

8 csatornás analóg erősítő PC -hez vagy otthoni színházhoz: 12 lépés (képekkel)

8 csatornás analóg erősítő PC -hez vagy Home Theatre -hez: Ez az első oktatható. Megtanítom, hogyan kell 8 csatornás erősítőt készíteni külön analóg kimenettel rendelkező számítógéphez vagy audiorendszerhez, asztali számítógépemhez, filmnézéshez, HD zenehallgatáshoz és játékok lejátszásához

Picaxe alapú digitális hőmérő max és min: 13 lépés

Picaxe alapú digitális hőmérő Max és Min értékekkel: (Kérjük, hagyjon üzenetet, de ne legyen túl kritikus, ez az első utasításom !!) Ez egy hőmérő, amelyet a lakóautónkhoz készítettem, a külső hőmérséklet megjelenítésére. Ez egy Picaxe chipen alapul, mivel olcsó és könnyen használható. Ha ez a