Tartalomjegyzék:

- Szerző John Day day@howwhatproduce.com.

- Public 2024-01-30 09:40.

- Utoljára módosítva 2025-01-23 14:47.

Csatlakoztassa Mojo fejlesztőlapját külső bemenetekhez ezzel az árnyékolással.

Mi az a Mojo fejlesztőtábla?

A Mojo fejlesztőtábla a Xilinx spartan 3 FPGA köré épülő fejlesztőlap. A táblát az Alchitry készítette. Az FPGA -k nagyon hasznosak, ha egyszerre több folyamatot kell végrehajtani.

Mire lesz szüksége?

Kellékek

Mojo fejlesztőtábla

Gerber reszelő

8 x 15 k ohmos ellenállás (opcionális*)

4 x 470 ohmos ellenállás

4 x 560 ohmos ellenállás

4 x CC hét szegmenses kijelző

4 x 3 mm -es LED

4 x SPDT tapintható kapcsoló

1 x 4 állású felszíni szerelésű DIP kapcsoló

2 x 25 x 2 vagy 4 x 25 fejléc

1x 2 x 5 tűs dobozfej

Forrasztópáka

Forrasztó

Fényáram

*(ha ezeket az ellenállásokat kihagyják, a belső húzást/lehúzást engedélyezni kell a megfelelő csapokhoz)

1. lépés: Töltse fel Gerber -t az Ön által választott PC -gyártóhoz

A tábláimhoz a JLC PCB -től rendeltem.

Az egyetlen változtatás az volt, hogy a színt a Mojo fekete színéhez akartam illeszteni.

2. lépés: A tábla összeszerelése

Forrasztáskor mindig hasznosnak találom, ha először a legalacsonyabb részeket forrasztjuk, így jó az ellenállásból kiindulni.

Az R5, R6, R7, R8, R9, R10, R11 és R12 15 k ohmos ellenállások, amelyeket a kapcsolók lehúzására használnak (ha belső felhúzást/lehúzást használ, ezt figyelmen kívül hagyja).

Az R1, R2, R3, R4 560 ohmos ellenállások, amelyek felelősek az áram korlátozásáért a 7 szegmenses kijelzőn.

Az R13, R14, R15, R16 470 ohmos ellenállások, amelyek felelősek az áram korlátozásáért a 4 LED -en keresztül.

A következő sorrendben forrasztja a merítőkapcsolót, a tapintható kapcsolókat, a LED -eket, a hét szegmenses kijelzőt és a dobozfej csatlakozóját.

Most helyezze a 25 x 2 (vagy 2 25 x 1) elemet a mojo -ba, hogy összeigazítsa a csapokat. Igazítsa a pajzsot a csapokhoz, és forrasztja a helyére.

3. lépés: Szoftver beállítása

Az Alchitry webhelyére hivatkozó szoftverek tájékoztatják Önt arról, hogy mire van szüksége az induláshoz és a Xilinx ISE telepítéséhez. Ha azonban megváltoztatja a.ucf fájlt, hogy tudja, milyen csapok vannak csatlakoztatva ahhoz, ami fontos a program futtatásához.

Itt van a.ucf fájl, amelyet a pajzzsal használok:

CONFIG VCCAUX = 3.3;

NET "clk" TNM_NET = clk; TIMESPEC TS_clk = PERIOD "clk" 50 MHz HIGH 50%; NET "clk" LOC = P56 | IOSTANDARD = LVTTL; NET "rst_n" LOC = P38 | IOSTANDARD = LVTTL; NET "cclk" LOC = P70 | IOSTANDARD = LVTTL; NET "spi_mosi" LOC = P44 | IOSTANDARD = LVTTL; NET "spi_miso" LOC = P45 | IOSTANDARD = LVTTL; NET "spi_ss" LOC = P48 | IOSTANDARD = LVTTL; NET "spi_sck" LOC = P43 | IOSTANDARD = LVTTL; NET "spi_channel" LOC = P46 | IOSTANDARD = LVTTL; NET "spi_channel" LOC = P61 | IOSTANDARD = LVTTL; NET "spi_channel" LOC = P62 | IOSTANDARD = LVTTL; NET "spi_channel" LOC = P65 | IOSTANDARD = LVTTL; NET "avr_tx" LOC = P55 | IOSTANDARD = LVTTL; NET "avr_rx" LOC = P59 | IOSTANDARD = LVTTL; NET "avr_rx_busy" LOC = P39 | IOSTANDARD = LVTTL; NET "Q [0]" LOC = P26 | IOSTANDARD = LVTTL; NET "Q [1]" LOC = P23 | IOSTANDARD = LVTTL; NET "Q [2]" LOC = P21 | IOSTANDARD = LVTTL; NET "Q [3]" LOC = P16 | IOSTANDARD = LVTTL; NET "S [0]" LOC = P7 | IOSTANDARD = LVTTL; NET "S [1]" LOC = P9 | IOSTANDARD = LVTTL; NET "S [2]" LOC = P11 | IOSTANDARD = LVTTL; NET "S [3]" LOC = P14 | IOSTANDARD = LVTTL; NET "pb [1]" LOC = P30 | IOSTANDARD = LVTTL; NET "pb [2]" LOC = P27 | IOSTANDARD = LVTTL; NET "pb [3]" LOC = P24 | IOSTANDARD = LVTTL; NET "pb [4]" LOC = P22 | IOSTANDARD = LVTTL; NET "sevsega [0]" LOC = P57 | IOSTANDARD = LVTTL; NET "sevsegb [0]" LOC = P58 | IOSTANDARD = LVTTL; NET "sevsegc [0]" LOC = P66 | IOSTANDARD = LVTTL; NET "sevsegd [0]" LOC = P67 | IOSTANDARD = LVTTL; NET "sevsege [0]" LOC = P74 | IOSTANDARD = LVTTL; NET "sevsegf [0]" LOC = P75 | IOSTANDARD = LVTTL; NET "sevsegg [0]" LOC = P78 | IOSTANDARD = LVTTL; NET "sevsegdp [0]" LOC = P80 | IOSTANDARD = LVTTL; NET "sevsega [1]" LOC = P82 | IOSTANDARD = LVTTL; NET "sevsegb [1]" LOC = P83 | IOSTANDARD = LVTTL; NET "sevsegc [1]" LOC = P84 | IOSTANDARD = LVTTL; NET "sevsegd [1]" LOC = P85 | IOSTANDARD = LVTTL; NET "sevsege [1]" LOC = P87 | IOSTANDARD = LVTTL; NET "sevsegf [1]" LOC = P88 | IOSTANDARD = LVTTL; NET "sevsegg [1]" LOC = P92 | IOSTANDARD = LVTTL; NET "sevsegdp [1]" LOC = P94 | IOSTANDARD = LVTTL; NET "sevsega [2]" LOC = P97 | IOSTANDARD = LVTTL; NET "sevsegb [2]" LOC = P98 | IOSTANDARD = LVTTL; NET "sevsegc [2]" LOC = P99 | IOSTANDARD = LVTTL; NET "sevsegd [2]" LOC = P100 | IOSTANDARD = LVTTL; NET "sevsege [2]" LOC = P101 | IOSTANDARD = LVTTL; NET "sevsegf [2]" LOC = P102 | IOSTANDARD = LVTTL; NET "sevsegg [2]" LOC = P104 | IOSTANDARD = LVTTL; NET "sevsegdp [2]" LOC = P111 | IOSTANDARD = LVTTL; NET "sevsega [3]" LOC = P114 | IOSTANDARD = LVTTL; NET "sevsegb [3]" LOC = P115 | IOSTANDARD = LVTTL; NET "sevsegc [3]" LOC = P116 | IOSTANDARD = LVTTL; NET "sevsegd [3]" LOC = P117 | IOSTANDARD = LVTTL; NET "sevsege [3]" LOC = P118 | IOSTANDARD = LVTTL; NET "sevsegf [3]" LOC = P119 | IOSTANDARD = LVTTL; NET "sevsegg [3]" LOC = P1120 | IOSTANDARD = LVTTL; NET "sevsegdp [3]" LOC = P121 | IOSTANDARD = LVTTL;

Ne feledje, ha nem telepítette a lehúzható ellenállásokat a.ucf -ben lévő csapok szerkesztéséhez

| LEHÚZ; o

| FELHÚZ;

Ha a blokkot bármire szeretné használni, a kapcsolatok a következők. A bal oldali a blokk pin száma, a jobb pedig a mojo pin szám, amelyet hozzá kell rendelnie.ucf fájljához:

pin 1 = 29

2. tüske = 51

3. csap = 32

4. tüske = 41

5 -ös csap = 34

6. csap = 35

7 -es csap = 40

8. tüske = 33

9 -es csap = GND

10 -es csap = +V

Ajánlott:

Olcsóbb ESP8266 WiFi pajzs Arduino és egyéb mikroszkópokhoz: 6 lépés (képekkel)

Olcsóbb ESP8266 WiFi pajzs Arduino és egyéb mikroszkópokhoz: Frissítés: 2020. október 29. Tesztelve az ESP8266 táblakönyvtár V2.7.4 verziójával - működik Frissítés: 2016. szeptember 23. Ne használja az Arduino ESP táblakönyvtárat V2.3.0 ehhez a projekthez. V2.2.0 működik

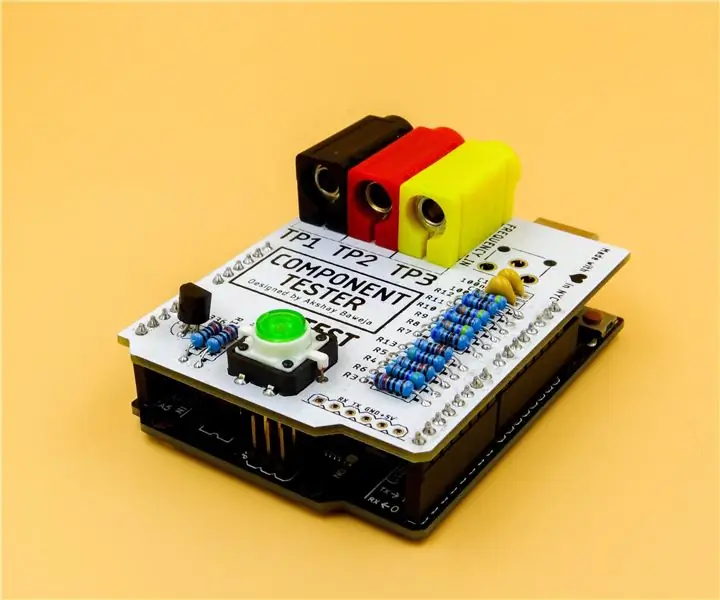

Komponens tesztelő UNO pajzs: 5 lépés (képekkel)

Komponens tesztelő UNO Shield: Hola Folks !! Korábbi komponens tesztelő projektjeimben - Komponens tesztelő kulcstartóban és USB komponens tesztelőben sok megjegyzést és üzenetet kaptam a komponens tesztelő Arduino kompatibilis verzióját kérve. A várakozásnak vége az emberek !!! C bemutatása

DIY ESP32 Fejlesztőtábla - ESPer: 5 lépés (képekkel)

DIY ESP32 Fejlesztési Testület - ESPer: Tehát a közelmúltban sok IoT -ről (tárgyak internetéről) olvastam, és bízz bennem, alig vártam, hogy kipróbálhassam ezeket a csodálatos eszközöket, amelyek képesek csatlakozni az internethez, magamat, és kezembe veszem a munkát. Szerencsére a lehetőség

JALPIC One Fejlesztőtábla: 5 lépés (képekkel)

JALPIC One Fejlesztési Tanács: Ha követi az Instructables projektjeimet, tudja, hogy nagy rajongója vagyok a JAL programozási nyelvnek a PIC mikrokontrollerrel kombinálva. A JAL egy Pascal-szerű programozási nyelv, amelyet a Microchip 8 bites PIC mikrokontrollereire fejlesztettek ki. Mo

UDuino: Nagyon alacsony költségű Arduino -kompatibilis fejlesztőtábla: 7 lépés (képekkel)

UDuino: Nagyon alacsony költségű Arduino -kompatibilis fejlesztőlap: Az Arduino táblák nagyszerűek a prototípusok készítéséhez. Ezek azonban meglehetősen drágák, ha több párhuzamos projektje van, vagy ha sok projektre van szüksége egy nagyobb projekthez. Vannak nagyszerű, olcsóbb alternatívák (Boarduino, Freeduino), de