Tartalomjegyzék:

- 1. lépés: Mi az a Vivado HLS?

- 2. lépés: HLS videókönyvtár

- 3. lépés: szintetizálás

- 4. lépés: Változtatás és egyéb információk az exportáláshoz

- 5. lépés: Exportálás Vivado IP könyvtárba

- 6. lépés: Szintézis és export elemzés

- 7. lépés: Az IP -könyvtár hozzáadása a Vivado -hoz

- 8. lépés: Frissítés végrehajtása

- 9. lépés: További részletek és információk

- 10. lépés: Kimenet és bemenet

- 11. lépés: AXI regisztrációs interfész

- 12. lépés: Adatfolyam -pragma

- Szerző John Day day@howwhatproduce.com.

- Public 2024-01-30 09:43.

- Utoljára módosítva 2025-01-23 14:48.

Szeretett volna valaha valós idejű videofeldolgozást végezni anélkül, hogy sok késést vagy beágyazott rendszert használna? Ehhez néha FPGA -kat (Field Programmable Gate Arrays) használnak; azonban a videófeldolgozási algoritmusok hardver -specifikációs nyelveken, például VHDL -ben vagy Verilogban történő írása a legjobb esetben frusztráló. Lépjen be a Vivado HLS -be, a Xilinx eszközbe, amely lehetővé teszi, hogy C ++ környezetben programozzon, és hardver -specifikációs nyelvkódot generáljon belőle.

Szükséges szoftverek:

- Vivado HLS

- Vivado

- (Ha az AXI regisztereket használja) Vivado SDK

(Nem kötelező) Töltse le a Xilinx által készített példákat itt:

Xilinx HLS videó példák

1. lépés: Mi az a Vivado HLS?

A Vivado HLS egy olyan eszköz, amelyet a c ++ típusú kódok FPGA -n megvalósítható hardverstruktúrákká alakítására használnak. Tartalmaz egy IDE -t a fejlesztéshez. Miután befejezte a HLS kód fejlesztését, exportálhatja a létrehozott IP -t formátumban Vivadóval való használatra.

Töltse le a csatolt fájlokat, és tegye a projekt létrehozása helyéhez. (nevezze át őket "top.cpp" és "top.h" névre, ha véletlenszerű nevük van)

2. lépés: HLS videókönyvtár

A HLS Videokönyv ebben a cikkben referenciatervekkel ellátott dokumentációt tartalmaz: XAPP1167A másik jó forrás a Xilinx Wiki oldal.

Indítsa el a Vivado HLS -t.

Hozzon létre egy új projektet.

Vegye ki az előző lépésben letöltött fájlokat, és adja hozzá forrásfájlokként. (Megjegyzés: a fájlok nem másolódnak be a projektbe, hanem helyükön maradnak.)

Ezután a Tallózás gombbal válassza ki a felső funkciót.

A következő oldalon válassza ki a használt Xilinx részt.

3. lépés: szintetizálás

Megoldás => Futtassa a C szintézist => Aktív megoldás

~ 227,218 másodperc múlva meg kell tenni. (Megjegyzés: a tényleges szintézisidő sok tényezőtől függően változik)

4. lépés: Változtatás és egyéb információk az exportáláshoz

A verziószámok kölcsönhatásba lépnek a Vivado -val, így frissítheti az IP -címet egy tervben. Ha ez egy kisebb verzióváltozás, akkor a helyén is elvégezhető, míg a főbb verzióváltozásokhoz manuálisan kell hozzáadnia az új blokkot, és eltávolítania a régit. Ha az interfészek nem változtak, és a verziófrissítés kicsi, a frissítés végrehajtható teljesen automatikusan történik az IP frissítés gomb megnyomásával. A "report_ip_status" parancsot futtathatja a Vivado tcl konzolban, hogy megtekinthesse az IP állapotát.

Állítsa be a verziószámokat és egyéb információkat a Solution => Solution Settings…

Alternatívaként ezeket a beállításokat az exportálás során is be lehet állítani.

5. lépés: Exportálás Vivado IP könyvtárba

Megoldás => RTL exportálása

Ha az előző lépésben nem állította be az IP -könyvtár részleteit, akkor most megteheti.

6. lépés: Szintézis és export elemzés

Ezen a képernyőn láthatjuk az exportált modulunkra vonatkozó statisztikákat, amelyek azt mutatják, hogy az megfelel a 10ns (100 MHz) órajel -periódusunknak és az egyes erőforrásokból.

Ennek, az összefoglaló jelentésünknek és az adatfolyam -elemzésünknek a kombinációjával láthatjuk, hogy 317338 óra ciklus * 10ns óraidő * 14 folyamat szakasz = 0,04442732 másodperc. Ez azt jelenti, hogy a képfeldolgozásunk által hozzáadott teljes késleltetés kevesebb, mint egy huszadik másodperc (ha a célzott 100 MHz -es órajelet használjuk).

7. lépés: Az IP -könyvtár hozzáadása a Vivado -hoz

A szintetizált IP -blokk használatához hozzá kell adnia a Vivado -hoz.

A Vivado-ban adjon hozzá egy IP-lerakatot a projekthez az IP-katalógusba lépéshez, és kattintson a jobb gombbal az "Adattár hozzáadása …" elemre.

Keresse meg a Vivado HLS projektkönyvtárát, és válassza ki a megoldáskönyvtárat.

Jelentenie kell a talált IP -t.

8. lépés: Frissítés végrehajtása

Néha módosítania kell a HLS blokkját, miután beillesztette azt a Vivado tervezésbe.

Ehhez elvégezheti a módosításokat, és újra szintetizálhatja és exportálhatja az IP -t egy magasabb verziószámmal (részleteket lásd a korábbi lépésekben a nagyobb/kisebb verziószám -változásokról).

Az új verzió exportálásának megváltoztatása után frissítse az IP -adattárait a Vivadóban. Ezt vagy akkor teheti meg, ha Vivado észreveszi, hogy az IP megváltozott a lerakatban, vagy manuálisan aktiválható. (Megjegyzés: ha az indítás után frissíti az IP -tárolókat, de mielőtt az exportálás befejeződik a HLS -ben, az IP ideiglenesen nem lesz ott, várja meg, amíg befejeződik, és frissítse újra.)

Ezen a ponton egy ablaknak kell megjelennie az információkkal arról, hogy egy IP -t megváltoztattak a lemezen, és lehetőséget ad arra, hogy frissítse azt a "Frissítés kiválasztva" gombbal. Ha a módosítás kisebb verzióváltozás volt, és egyik interfész sem változott, majd a gomb megnyomása automatikusan lecseréli a régi IP -t az újra, különben további munkára lehet szükség.

9. lépés: További részletek és információk

A következő lépések további információkat tartalmaznak a HLS szintézis működéséről és arról, hogy mit tehet vele.

Példa egy HLS szintetizált IP -blokkot használó projektre, lásd ezt az utasítást.

10. lépés: Kimenet és bemenet

A végső IP -blokk kimeneteit és bemeneteit a szintetizátor elemzése határozza meg az adatáramlásból a felső funkcióba.

A VHDL -hez vagy a veriloghoz hasonlóan a HLS lehetővé teszi az IP közötti kapcsolatok részleteinek megadását. Ezek a sorok példák erre:

void image_filter (AXI_STREAM & video_in, AXI_STREAM & video_out, int & x, int & y) {

#pragma HLS INTERFACE tengely port = video_in bundle = INPUT_STREAM #pragma HLS INTERFACE tengely port = video_out bundle = OUTPUT_STREAM #pragma HLS INTERFACE s_axilite port = x bundle = CONTROL_BUS offset = 0x14 #pragma H_x bite

Láthatja, hogy ezek az irányelvek hogyan befolyásolják az IP -blokkon megjelenített portokat.

11. lépés: AXI regisztrációs interfész

Annak érdekében, hogy bemenetet/kimenetet kapjon az IP -blokkból a PS -hez, jó módja ennek az AXI interfészen keresztül.

Ezt megadhatja a HLS -kódjában, beleértve az értékek későbbi eléréséhez használandó eltolásokat is:

void image_filter (AXI_STREAM & video_in, AXI_STREAM & video_out, int & x, int & y) {

#pragma HLS INTERFACE s_axilite port = x köteg = CONTROL_BUS offset = 0x14

#pragma HLS INTERFACE s_axilite port = y bundle = CONTROL_BUS offset = 0x1C #pragma HLS adatfolyam

x = 42;

y = 0xHUHATÓ; }

Miután megfelelően csatlakozott a Vivado -hoz, az értékeket a Vivado SDK ezen kódjával érheti el:

#include "paraméterek.h"

#define xregoff 0x14 #define yregoff 0x1c x = Xil_In32 (XPAR_IMAGE_FILTER_0_S_AXI_CONTROL_BUS_BASEADDR+xregoff); y = Xil_In32 (XPAR_IMAGE_FILTER_0_S_AXI_CONTROL_BUS_BASEADDR+yregoff);

Ennek eredményeként 42 x -el és 0xdeadbeef lesz y -ban

12. lépés: Adatfolyam -pragma

A #pragma DATAFLOW -ban a kód végrehajtásának módja megváltozik a normál C ++ - ról. A kód csövezett, így az összes utasítás mindig fut az adatok különböző részein (gondoljon rá úgy, mint egy gyári futószalagra, minden állomás folyamatosan dolgozik, és egy funkciót végez, és továbbítja a következő állomásnak)

a képen látható, hogy az egyes irányelvek

Annak ellenére, hogy normális változónak tűnnek, az img objektumok valójában kis pufferként valósulnak meg a parancsok között. Ha egy képet bemenetként használunk egy függvényhez, "elfogyasztja" azt, és többé nem használható. (Ezért szükség van az ismétlődő parancsokra)

Ajánlott:

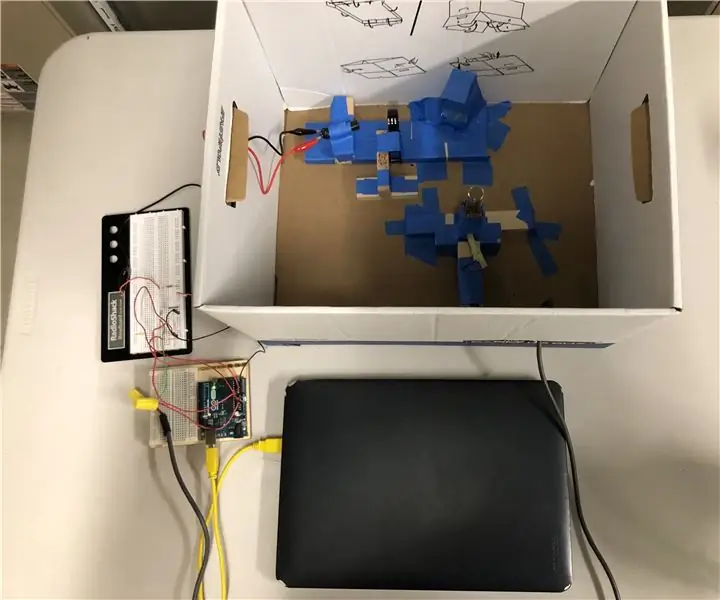

Házi készítésű Jenga blokk spektrofotométer algák kísérleteihez: 15 lépés

Házi készítésű Jenga blokk spektrofotométer algák kísérleteihez: Az algák fotoszintetikus protisták, és mint ilyenek, kritikus élőlények a vízi táplálékláncokban. A tavaszi és nyári hónapokban azonban ezek és más mikroorganizmusok megsokszorozhatják és eláraszthatják a természetes vízkészleteket, ami oxigénhiányhoz vezethet

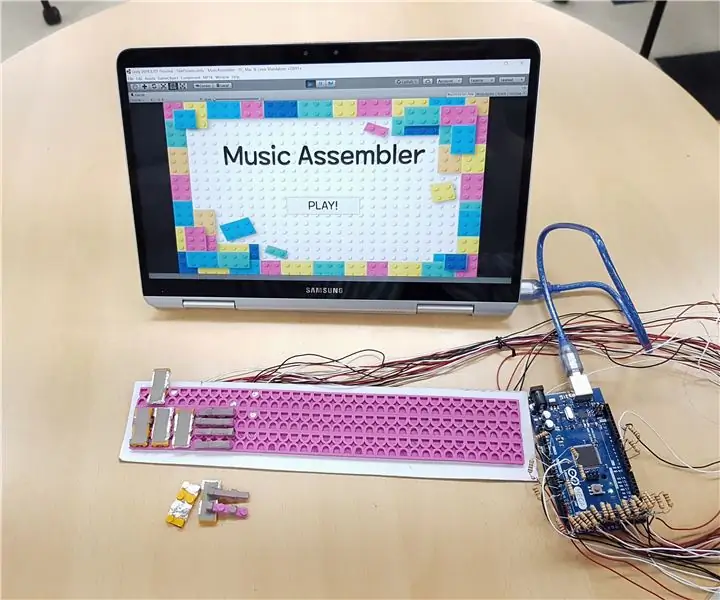

Music Assembler: Integrált virtuális hangszer blokk típusú érintőérzékelővel: 4 lépés

Music Assembler: Integrált virtuális hangszer blokk-típusú érintőérzékelővel: Sokan szeretnének megtanulni hangszeren játszani. Sajnos néhányan nem kezdik el a műszerek magas ára miatt. Ennek alapján úgy döntöttünk, hogy integrált virtuális hangszerrendszert készítünk, hogy csökkentsük a kezdeti költségvetést

Retro beszéd szintézis. Rész: 12 IoT, otthoni automatizálás: 12 lépés (képekkel)

Retro beszéd szintézis. Rész: 12 IoT, otthonautomatizálás: Ez a cikk a 12. az otthoni automatizálásról szóló utasításokban, amelyek dokumentálják, hogyan lehet létrehozni és integrálni egy IoT Retro beszédszintetizáló eszközt egy meglévő otthoni automatizálási rendszerbe, beleértve az összes szükséges szoftverfunkciót, amely lehetővé teszi a

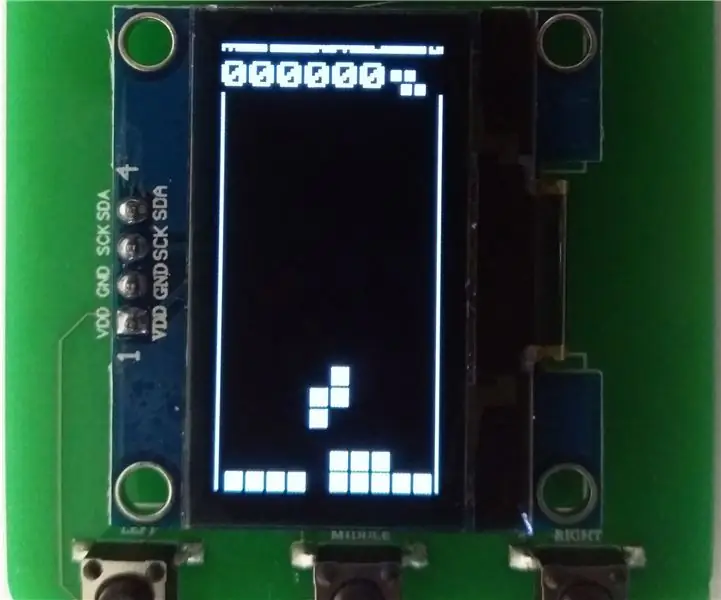

Blokk játék: 3 lépés

Blokkjáték: Ezt a pockeTETRIS projekt ihlette. Szerettem volna olyan áramköri lapot, amely nagyobb képernyőt használ, kényelmesebbé teszi a játékot tok nélkül, és be- és ki kapcsolót

Az E-blokk transzformátor szétszerelése: 6 lépés

Szerelje szét az E-blokk transzformátort: terveztem gitárfelvételt készíteni, de hiányzott a zománcozott huzal. Arra törekedtem, hogy megpróbáljam elkészíteni anélkül, hogy bármit is vásárolnék, egy ideig gondolkodtam, és eszembe jutott, hogy kiveszem a régi antennaforgatóm transzformátorából. Sajnos a g