Tartalomjegyzék:

- Szerző John Day day@howwhatproduce.com.

- Public 2024-01-30 09:41.

- Utoljára módosítva 2025-01-23 14:47.

Lenyűgöznek azok a válaszok, amelyeket ebben a blogban kapok. Köszönöm srácok, hogy meglátogatták a blogomat, és motiváltak, hogy megosszam veletek tudásomat. Ezúttal egy másik érdekes modul tervét mutatom be, amelyet minden SOC -ban látunk - Interrupt Controller.

Egy egyszerű, mégis hatékony programozható megszakításvezérlőt tervezünk. Ez egy teljesen konfigurálható és paraméterezett kialakítás, amely platformokon keresztül hordozható. Ezt azután terveztem, hogy sokat olvastam néhány népszerű megszakításvezérlő architektúrán, mint például az NVIC, 8259a, RISC-V PLIC, a Microblaze INTC stb. megszakításvezérlő segítségével.

1. lépés: Specifikációk

Az IP specifikációi a következők:

- AHB3-Lite interfész.

-

Statikusan konfigurálható paraméterek:

- Külső megszakító források száma; 63 megszakítást támogat.

- Prioritási szintek száma; 63 szintet támogat.

- Fészkelési szintek száma; akár 8 szintű fészkelést támogat.

- Busz szélessége; 32 vagy 64.

- Globálisan és lokálisan maszkolható megszakítások.

- Dinamikusan konfigurálható prioritási szint minden megszakításhoz.

- Két működési mód - teljesen beágyazott és egyenlő prioritású mód.

- Támogatja az aktív, magas szintű érzékeny megszakításokat.

A tervezés során a RISC-V PLIC specifikációk által ihletett megszakító kézfogó mechanizmust alkalmazzák.

A megszakítás elővásárlását a 8259a ihlette

További olvasmányok: Microblaze INTC, NVIC

2. lépés: A PIC áttekintése

A programozható megszakításvezérlő (PIC) több megszakítást fogad a külső perifériáktól, és egyesíti azokat egyetlen megszakítási kimenetben a célprocesszor magjához.

A PIC vezérlése vezérlő- és állapotregisztereken keresztül történik. Minden PIC regiszter memórialeképezett, és az AHB3-Lite busz interfészen keresztül érhető el.

A nyilvántartó bank a megszakításvezérlőkre jellemző konfigurációs nyilvántartásból, engedélyező regiszterekből, függőben lévő nyilvántartásokból, üzemi nyilvántartásokból, elsőbbségi regiszterekből és azonosító regiszterekből áll.

A konfigurációs regiszter a PIC működési módjának beállítására szolgál. Teljesen beágyazott vagy egyenlő prioritású módban is működhet.

Minden megszakításhoz hozzárendelhetők prioritások és egyedileg maszkolható. Az összes megszakítás globális maszkolása is támogatott.

A nyilvántartó bank kölcsönhatásba lép a Priority Resolverrel és a BTC-vel (Binary-Tree-Comparator), hogy megoldja a függőben lévő megszakítások prioritásait, és ennek megfelelően érvényesítse a megszakítást. Az azonosító regiszter tartalmazza a legmagasabb prioritású megszakítás függvényében az azonosítót.

3. lépés: RTL tervezés és megvalósítás

A PIC tervezése a prioritások megoldásának késleltetésének csökkentésére helyezi a hangsúlyt, ami a tervezés legidőigényesebb része. Mivel a tervezés egyetlen órajelciklusban oldja meg a prioritásokat, a teljesítmény romlik a Log2 komplexitású források számának növekedésével.

A tervezést sikeresen végrehajtották, és az időzítést a következő frekvenciákig ellenőrizték az Artix-7 FPGA-n.

- Akár 15 forrás: 100 MHz

- Akár 63 forrás: 50 MHz

Csak a PIC által hozzáadott megszakítási késleltetés 3 óra ciklus (kivéve a processzor kontextusváltási idejét és az első ISR utasítás lekérési idejét).

4. lépés: Fontos megjegyzések és csatolt fájlok

Fontos jegyzetek:

- Ha az AHB3-Lite interfész nem kívánatos, megváltoztathatja a felső modult, és használhatja a PIC vázszerkezetét. A mellékelt tesztpad azonban IP-hez készült, AHB3-Lite interfésszel.

- A PIC IP v1.0 teljesen hordozható, csupasz RTL kialakítás.

- Funkcionálisan igazolt, hogy mindkét módban működik.

Csatolt fájlok:

- Tervezési kódok és tesztpad VHDL -ben.

- Teljes IP dokumentáció.

Ez egy nyílt forráskódú kivitel… Nyugodtan használhatja…

Bármilyen kérdés esetén, bármikor:

Mitu Raj

Ajánlott:

Jelenlegi módú oszcillátor tervezése D osztályú audioerősítőkhöz: 6 lépés

Jelenlegi módú oszcillátor tervezése a D osztályú audioerősítőkhöz: Az elmúlt években a D osztályú audioerősítők váltak a hordozható audiorendszerek, például az MP3 és a mobiltelefonok előnyös megoldásává nagy hatékonyságuk és alacsony energiafogyasztásuk miatt. Az oszcillátor a D osztály fontos része

LoRa-alapú vizuális mezőgazdasági monitoring rendszer Iot - Előlapi alkalmazás tervezése Firebase és Angular használatával: 10 lépés

LoRa-alapú vizuális mezőgazdasági monitoring rendszer Iot | Előlapi alkalmazás tervezése a Firebase & Angular használatával: Az előző fejezetben arról beszéltünk, hogy az érzékelők hogyan működnek a loRa modullal a firebase Realtime adatbázis feltöltéséhez, és láttuk a nagyon magas szintű diagramot, hogyan működik az egész projektünk. Ebben a fejezetben arról fogunk beszélni, hogyan lehet

FPV akadálypálya készítése és tervezése quadcopterekhez: 6 lépés

Hogyan készítsünk és tervezzünk FPV akadálypályát quadcopterekhez: Tehát egy ideje repültem a hátsó udvaromban a lárvámmal x, és nagyon szórakoztató volt. Annyira jól szórakoztam, hogy elértem azt a pontot, amikor kicsit bonyolultabbá akartam tenni a dolgokat, mert túl könnyűnek éreztem magam. Kitaláltam egy tervet egy fpv tanfolyamra

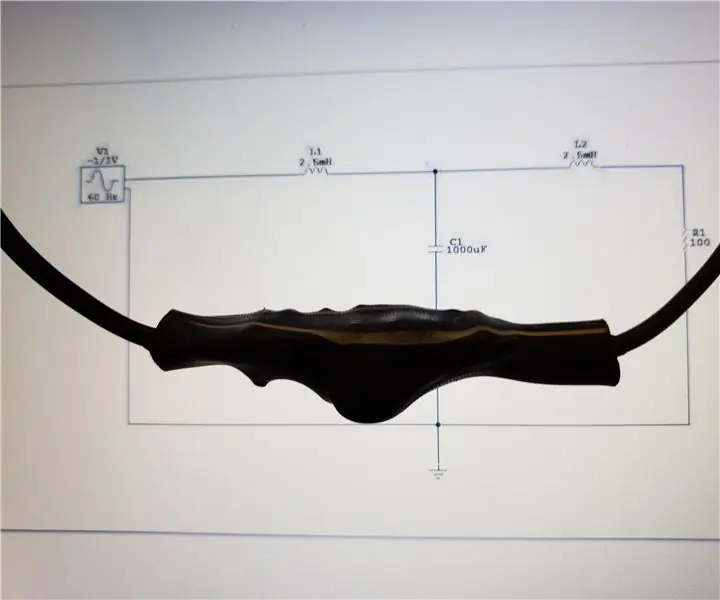

Tápvezeték szűrő tervezése és építése Android telefon töltőhöz: 5 lépés

Tápvezeték -szűrő tervezése és megépítése Android telefon töltőhöz: Ebben az utasításban megmutatom, hogyan kell szabványos USB -kábelt mini USB -kábellel elválasztani, középen elválasztani, és behelyezni egy szűrőáramkört, amely csökkenti a túlzott zajt vagy hash, amelyet egy tipikus androidos tápegység állít elő. Van egy hordozható m

Egyszerű VGA vezérlő tervezése VHDL és Verilog formátumban: 5 lépés

Egyszerű VGA vezérlő tervezése VHDL és Verilog formátumban: Ebben az utasításban egy egyszerű VGA vezérlőt tervezünk RTL -ben. A VGA Controller egy digitális áramkör, amelyet VGA kijelzők meghajtására terveztek. A keretpufferből (VGA memória) olvas, amely a megjelenítendő keretet képviseli, és létrehozza a szükséges